AXI总线简介

0.绪论

AXI是高级扩展接口,在AMBA3.0中提出,AMBA4.0将其修改升级为AXI4.0。AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream

AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

1.简介

1.1 关于AXI协议

AMBA AXI协议支持支持高性能、高频率系统设计。

- 适合高带宽低延时设计

- 无需复杂的桥就能实现高频操作

- 能满足大部分器件的接口要求

- 适合高初始延时的存储控制器

- 提供互联架构的灵活性与独立性

- 向下兼容已有的AHB和APB接口

关键特点:

- 分离的地址/控制、数据相位

- 使用字节线来支持非对齐的数据传输

- 使用基于burst的传输,只需传输首地址

- 分离的读、写数据通道,能提供低功耗DMA

- 支持多种寻址方式

- 支持乱序传输

- 允许容易的添加寄存器级来进行时序收敛

1.2 AXI架构

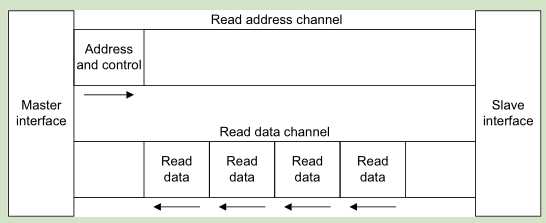

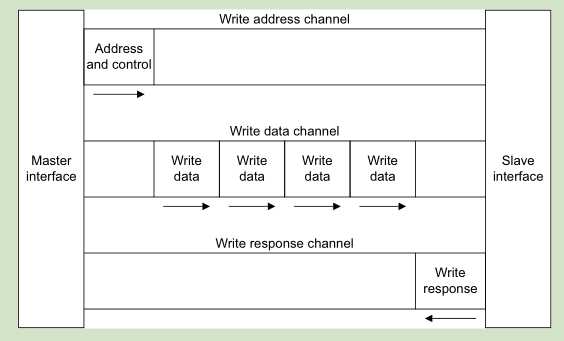

AXI协议是基于burst的传输,并且定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

地址通道携带控制消息用于描述被传输的数据属性,数据传输使用写通道来实现“主”到“从”的传输,“从”使用写响应通道来完成一次写传输;读通道用来实现数据从“从”到“主”的传输。

图 1-1 读架构

图 1-2 写架构

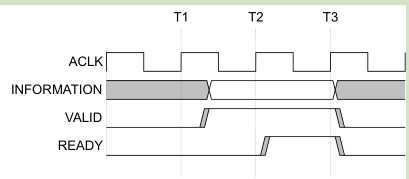

AXI是基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024bit)和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,“主”无需等待“从”对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16...1024bit)和字节线(用于指示8bit 数据信号的有效性)。

写响应通道:“从”使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

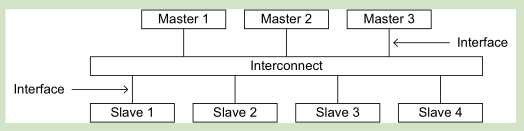

图 1-3 接口与互联

AXI协议提供单一的接口定义,能用在下述三种接口之间:master/interconnect、slave/interconnect、master/slave。

可以使用以下几种典型的系统拓扑架构:

- 共享地址与数据总线

- 共享地址总线,多数据总线

- multilayer多层,多地址总线,多数据总线

在大多数系统中,地址通道的带宽要求没有数据通道高,因此可以使用共享地址总线,多数据总线结构来对系统性能和互联复杂度进行平衡。

寄存器片(Register Slices):

每个AXI通道使用单一方向传输信息,并且各个通道直接没有任何固定关系。因此可以可以在任何通道任何点插入寄存器片,当然这会导致额外的周期延迟。

使用寄存器片可以实现周期延迟(cycles of latency)和最大操作频率的折中;使用寄存器片可以分割低速外设的长路径。

2.信号描述

表 2-1 全局信号

| 信号名 | 源 | 描述 |

| ACLK | 时钟源 | 全局时钟信号 |

| ARESETn | 复位源 | 全局复位信号,低有效 |

表 2-2 写地址通道信号

| 信号名 | 源 | 描述 |

| AWID | 主机 | 写地址ID,用来标志一组写信号 |

| AWADDR | 主机 | 写地址,给出一次写突发传输的写地址 |

| AWLEN | 主机 | 突发长度,给出突发传输的次数 |

| AWSIZE | 主机 | 突发大小,给出每次突发传输的字节数 |

| AWBURST | 主机 | 突发类型 |

| AWLOCK | 主机 | 总线锁信号,可提供操作的原子性 |

| AWCACHE | 主机 | 内存类型,表明一次传输是怎样通过系统的 |

| AWPROT | 主机 | 保护类型,表明一次传输的特权级及安全等级 |

| AWQOS | 主机 | 质量服务QoS |

| AWREGION | 主机 | 区域标志,能实现单一物理接口对应的多个逻辑接口 |

| AWUSER | 主机 | 用户自定义信号 |

| AWVALID | 主机 | 有效信号,表明此通道的地址控制信号有效 |

| AWREADY | 从机 | 表明“从”可以接收地址和对应的控制信号 |

表 2-3 写数据通道信号

| 信号名 | 源 | 描述 |

| WID | 主机 | 一次写传输的ID tag |

| WDATA | 主机 | 写数据 |

| WSTRB | 主机 | 写数据有效的字节线,用来表明哪8bits数据是有效的 |

| WLAST | 主机 | 表明此次传输是最后一个突发传输 |

| WUSER | 主机 | 用户自定义信号 |

| WVALID | 主机 | 写有效,表明此次写有效 |

| WREADY | 从机 | 表明从机可以接收写数据 |

表 2-4 写响应通道信号

| 信号名 | 源 | 描述 |

| BID | 从机 | 写响应ID tag |

| BRESP | 从机 | 写响应,表明写传输的状态 |

| BUSER | 从机 | 用户自定义 |

| BVALID | 从机 | 写响应有效 |

| BREADY | 主机 | 表明主机能够接收写响应 |

表 2-5 读地址通道信号

| 信号名 | 源 | 描述 |

| ARID | 主机 | 读地址ID,用来标志一组写信号 |

| ARADDR | 主机 | 读地址,给出一次写突发传输的读地址 |

| ARLEN | 主机 | 突发长度,给出突发传输的次数 |

| ARSIZE | 主机 | 突发大小,给出每次突发传输的字节数 |

| ARBURST | 主机 | 突发类型 |

| ARLOCK | 主机 | 总线锁信号,可提供操作的原子性 |

| ARCACHE | 主机 | 内存类型,表明一次传输是怎样通过系统的 |

| ARPROT | 主机 | 保护类型,表明一次传输的特权级及安全等级 |

| ARQOS | 主机 | 质量服务QoS |

| ARREGION | 主机 | 区域标志,能实现单一物理接口对应的多个逻辑接口 |

| ARUSER | 主机 | 用户自定义信号 |

| ARVALID | 主机 | 有效信号,表明此通道的地址控制信号有效 |

| ARREADY | 从机 | 表明“从”可以接收地址和对应的控制信号 |

表 2-6 读数据通道信号

| 信号名 | 源 | 描述 |

| RID | 从机 | 读ID tag |

| RDATA | 从机 | 读数据 |

| RRESP | 从机 | 读响应,表明读传输的状态 |

| RLAST | 从机 | 表明读突发的最后一次传输 |

| RUSER | 从机 | 用户自定义 |

| RVALID | 从机 | 表明此通道信号有效 |

| RREADY | 主机 | 表明主机能够接收读数据和响应信息 |

表 2-7 低功耗接口信号

| 信号名 | 源 | 描述 |

| CSYSREQ | 时钟控制器 | 系统退出低功耗请求,此信号从“时钟控制器”到“外设” |

| CSYSACK | 外设 | 退出低功耗状态确认 |

| CACTIVE | 外设 | 外设请求时钟有效 |

3.信号接口要求

3.1时钟复位

时钟

每个AXI组件使用一个时钟信号ACLK,所有输入信号在ACLK上升沿采样,所有输出信号必须在ACLK上升沿后发生。

复位

AXI使用一个低电平有效的复位信号ARESETn,复位信号可以异步断言,但必须和时钟上升沿同步去断言。

复位期间对接口有如下要求:①主机接口必须驱动ARVALID,AWVALID,WVALID为低电平;②从机接口必须驱动RVALID,BVALID为低电平;③所有其他信号可以被驱动到任意值。

在复位后,主机可以在时钟上升沿驱动ARVALID,AWVALID,WVALID为高电平。

3.2基本读写传输

握手过程

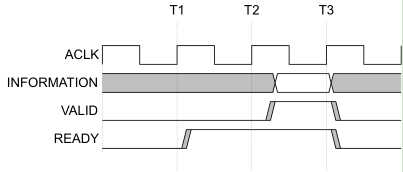

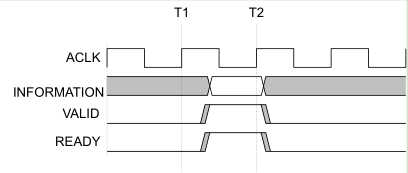

5个传输通道均使用VALID/READY信号对传输过程的地址、数据、控制信号进行握手。使用双向握手机制,传输仅仅发生在VALID、READY同时有效的时候。下图是几种握手机制:

图 3-1 VALID before READY 握手

图 3-2 READY before VALID 握手

图 3-3 VALID with READY 握手

通道信号要求

通道握手信号:每个通道有自己的xVALID/xREADY握手信号对。

写地址通道:当主机驱动有效的地址和控制信号时,主机可以断言AWVALID,一旦断言,需要保持AWVALID的断言状态,直到时钟上升沿采样到从机的AWREADY。AWREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言AWVALID,一个用来断言AWREADY);当AWREADY为高时,从机必须能够接受提供给它的有效地址。

写数据通道:在写突发传输过程中,主机只能在它提供有效的写数据时断言WVALID,一旦断言,需要保持断言状态,知道时钟上升沿采样到从机的WREADY。WREADY默认值可以为高,这要求从机总能够在单个周期内接受写数据。主机在驱动最后一次写突发传输是需要断言WLAST信号。

写响应通道:从机只能它在驱动有效的写响应时断言BVALID,一旦断言需要保持,直到时钟上升沿采样到主机的BREADY信号。当主机总能在一个周期内接受写响应信号时,可以将BREADY的默认值设为高。

读地址通道:当主机驱动有效的地址和控制信号时,主机可以断言ARVALID,一旦断言,需要保持ARVALID的断言状态,直到时钟上升沿采样到从机的ARREADY。ARREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言ARVALID,一个用来断言ARREADY);当ARREADY为高时,从机必须能够接受提供给它的有效地址。

读数据通道:只有当从机驱动有效的读数据时从机才可以断言RVALID,一旦断言需要保持直到时钟上升沿采样到主机的BREADY。BREADY默认值可以为高,此时需要主机任何时候一旦开始读传输就能立马接受读数据。当最后一次突发读传输时,从机需要断言RLAST。

通道间关系

AXI协议要求通道间满足如下关系:

- 写响应必须跟随最后一次burst的的写传输

- 读数据必须跟随数据对应的地址

- 通道握手信号需要确认一些依耐关系

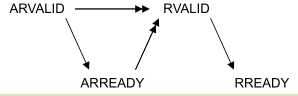

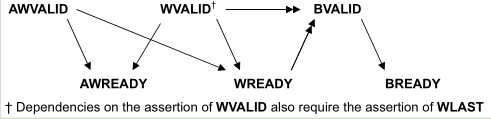

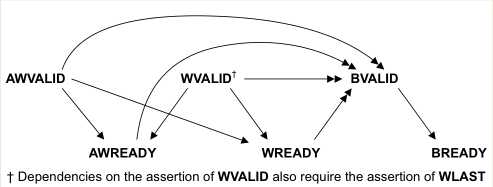

通道握手信号的依耐关系

为防止死锁,通道握手信号需要遵循一定的依耐关系。①VALID信号不能依耐READY信号。②AXI接口可以等到检测到VALID才断言对应的READY,也可以检测到VALID之前就断言READY。下面有几个图表明依耐关系,单箭头指向的信号能在箭头起点信号之前或之后断言;双箭头指向的信号必须在箭头起点信号断言之后断言。

图 3-4 读传输握手依耐关系

图 3-5 写传输握手依耐关系

图 3-6 从机写响应握手依耐关系

3.3传输结构

地址结构

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

1)突发长度

ARLEN[7:0]决定读传输的突发长度,AWLEN[7:0]决定写传输的突发长度。AXI3只支持1~16次的突发传输(Burst_length=AxLEN[3:0]+1),AXI4扩展突发长度支持INCR突发类型为1~256次传输,对于其他的传输类型依然保持1~16次突发传输(Burst_Length=AxLEN[7:0]+1)。

burst传输具有如下规则:

- wraping burst ,burst长度必须是2,4,8,16

- burst不能跨4KB边界

- 不支持提前终止burst传输

所有的组件都不能提前终止一次突发传输。然而,主机可以通过解断言所有的写的strobes来使非所有的写字节来减少写传输的数量。读burst中,主机可以忽略后续的读数据来减少读个数。也就是说,不管怎样,都必须完成所有的burst传输。

注:对于FIFO,忽略后续读数据可能导致数据丢失,必须保证突发传输长度和要求的数据传输大小匹配。

突发大小

ARSIZE[2:0],读突发传输;AWSIZE[2:0],写突发传输。

AxSIZE[2:0] bytes in transfer

‘b000 1

‘b001 2

‘b010 4

‘b011 8

‘b100 16

‘b101 32

‘b110 64

‘b111 128

突发类型

FIXED:突发传输过程中地址固定,用于FIFO访问

INCR:增量突发,传输过程中,地址递增。增加量取决AxSIZE的值。

WRAP:回环突发,和增量突发类似,但会在特定高地址的边界处回到低地址处。回环突发的长度只能是2,4,8,16次传输,传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。回环边界等于(AxSIZE*AxLEN)。

AxBURST[1:0] burst type

‘b00 FIXED

‘b01 INCR

‘b10 WRAP

‘b11 Reserved

Start_Address=AxADDR

Number_Bytes=2^AxSIZE

Burst_Length=AxLEN+1

Aligned_Addr=(INT(Start_Address/Number_Bytes))xNumber_Bytes。//INT表示向下取整。

对于INCR突发和WRAP突发但没有到达回环边界,地址由下述方程决定:

Address_N=Aligned_Address+(N-1)xNumber_Bytes

WRAP突发,突发边界:

Wrap_Boundary=(INT(Start_Address/(Number_Bytes x Burst_Length)))x(Number_Bytes x Burst_Length)

数据读写结构

WSTRB[n:0]对应于对应的写字节,WSTRB[n]对应WDATA[8n+7:8n]。WVALID为低时,WSTRB可以为任意值,WVALID为高时,WSTRB为高的字节线必须指示有效的数据。

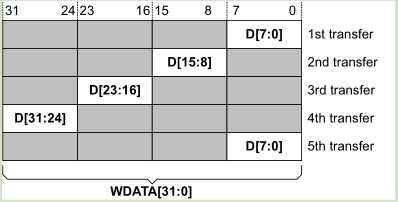

窄传输

当主机产生比它数据总线要窄的传输时,由地址和控制信号决定哪个字节被传输:

INCR和WRAP,不同的字节线决定每次burst传输的数据,FIXED,每次传输使用相同的字节线。

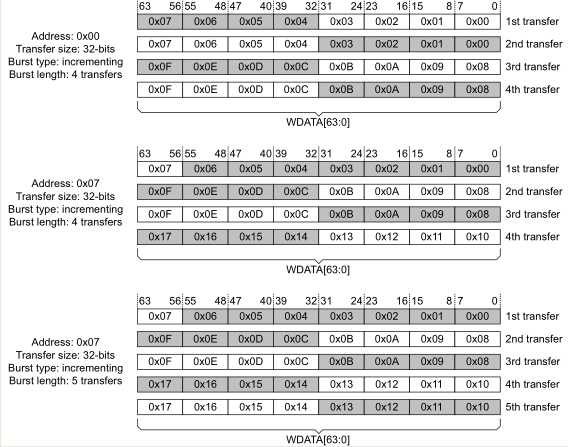

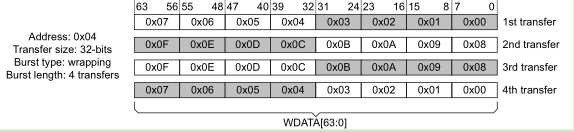

下图给出了5次突发传输,起始地址为0,每次传输为8bit,数据总线为32bit,突发类型为INCR。

图 3-7 窄传输示例1

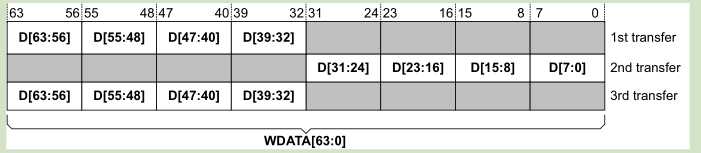

下图给出3次突发,起始地址为4,每次传输32bit,数据总线为64bit。

图 3-8 窄传输示例2

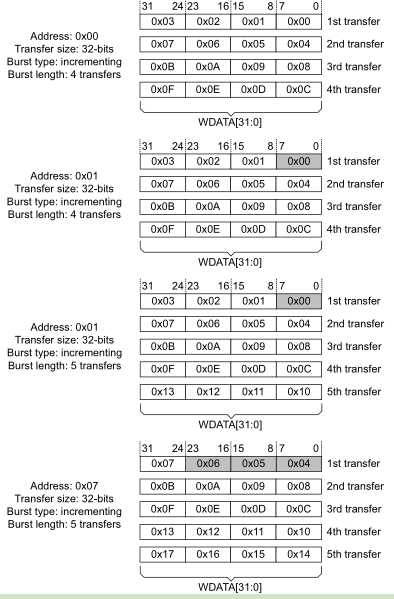

非对齐传输

AXI支持非对齐传输。在大于一个字节的传输中,第一个自己的传输可能是非对齐的。如32-bit数据包起始地址在0x1002,非32bit对齐。

主机可以①使用低位地址线来表示非对齐的起始地址;②提供对齐的起始地址,使用字节线来表示非对齐的起始地址。

图 3-9 对齐非对齐传输示例1-32bit总线

图 3-10 对齐非对齐传输示例2-64bit总线

图 3-11 对齐的回环传输示例

读写响应结构

读传输的响应信息是附加在读数据通道上的,写传输的响应在写响应通道。

RRESP[1:0],读传输

BRESP[1:0],写传输

OKAY(‘b00):正常访问成功

EXOKAY(‘b01):Exclusive 访问成功

SLVERR(‘b10):从机错误。表明访问已经成功到了从机,但从机希望返回一个错误的情况给主机。

DECERR(‘b11):译码错误。一般由互联组件给出,表明没有对应的从机地址。