蛋疼的 qii 神马警告才是需要注意的警告?(由于警告引起的截然不同的运行结果)

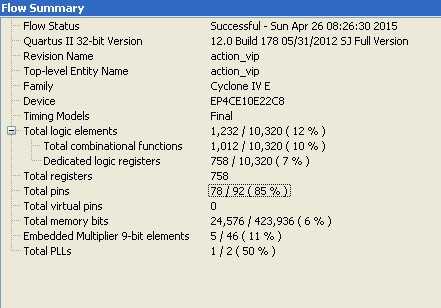

移植了一份程序,之前工程是Cyclone II 后来换成 Cyclone IV E EP4CE10E22C8

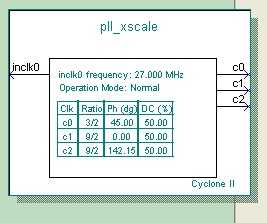

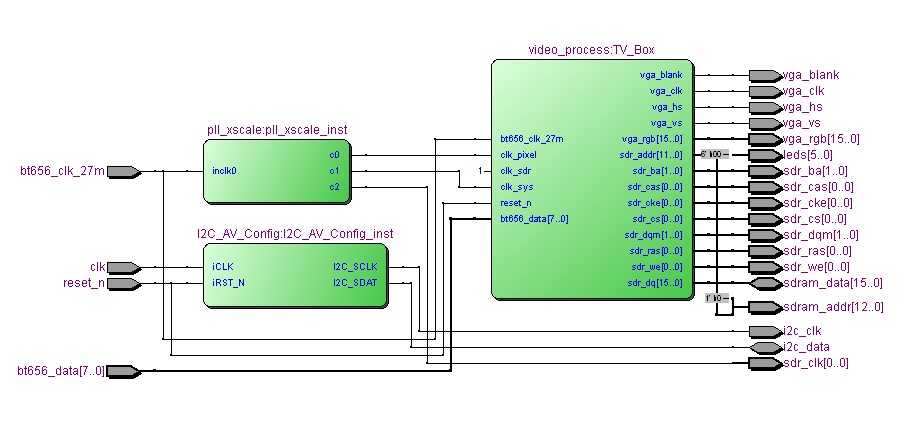

用到的资源:pll,sdram,vga

移植办法:

1、更改工程配置,重新选择ic

2、重新分配管脚

3、编译下载至目标板

4、运行ok

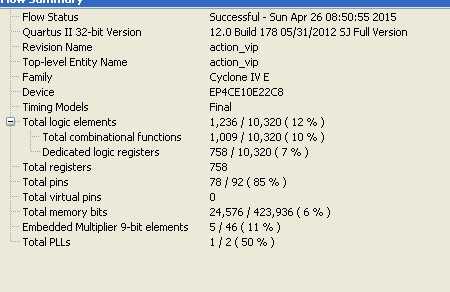

以下是这个项目的一些重要信息

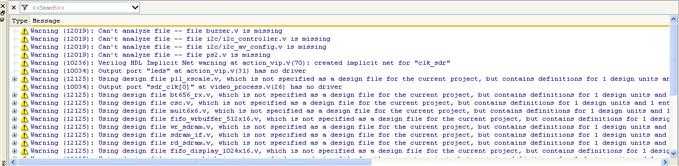

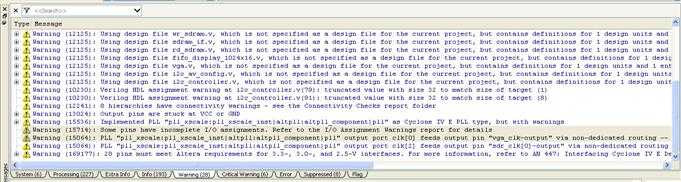

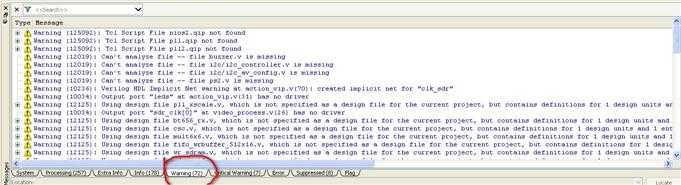

再看看警告

如此蛋疼的警告,虽然28个但是确实不影响使用

再看看运行结果,确实不错,没有问题,唯一的问题,就是需要多次复位才能正常

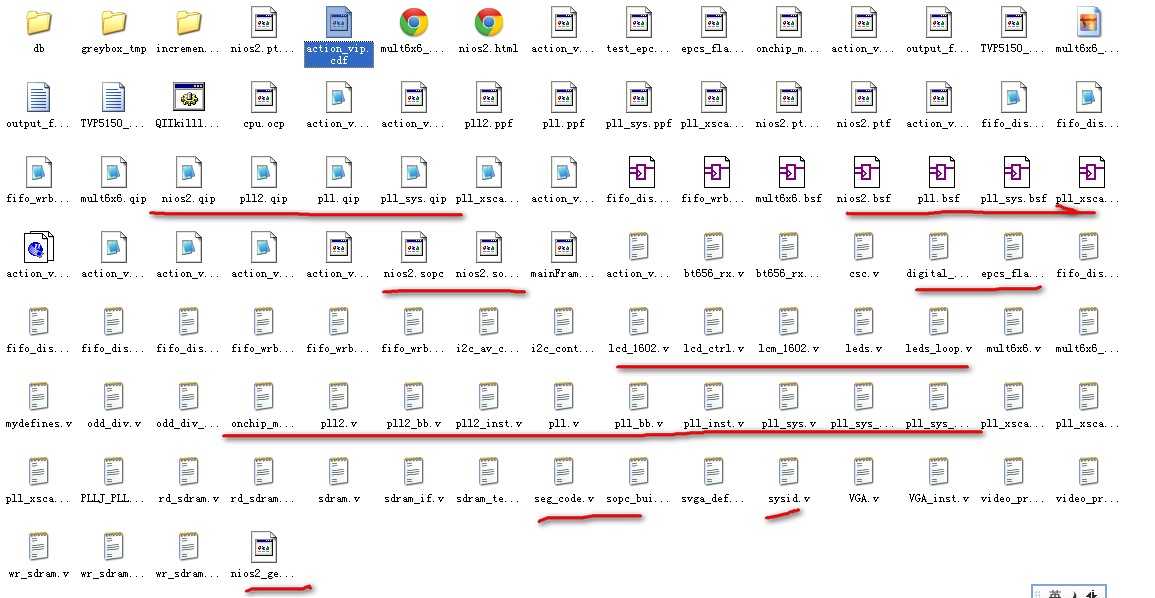

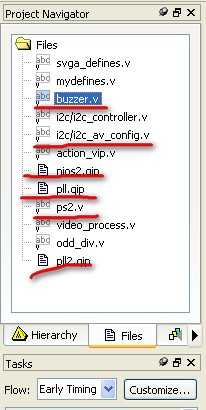

再看看这一堆蛋疼的垃圾文件,都是无用,看着让人心烦。果断删除

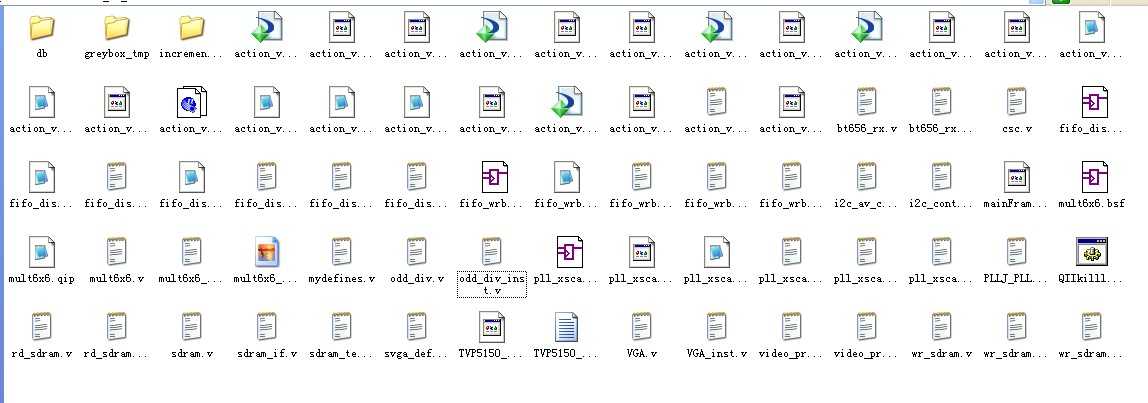

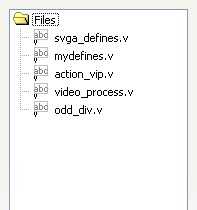

删除后结果

重新编译:发现有变化

1、资源消耗发生变化。

2、警告数量发生变化

下载运行,已经全然无反应了,无法工作,继续研究!!

垃圾无用的包含文件,果断删除

重新编译!!

警告数减少,依然无法正常工作!!

看看是神马警告

Warning (10236): Verilog HDL Implicit Net warning at action_vip.v(70): created implicit net for "clk_sdr"

Warning (10034): Output port "leds" at action_vip.v(31) has no driver

Warning (12125): Using design file pll_xscale.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: pll_xscale

Info (12023): Found entity 1: pll_xscale

Warning (10034): Output port "sdr_clk[0]" at video_process.v(26) has no driver

Warning (12125): Using design file bt656_rx.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: bt656_rx

Info (12023): Found entity 1: bt656_rx

Warning (12125): Using design file csc.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: csc

Info (12023): Found entity 1: csc

Warning (12125): Using design file mult6x6.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: mult6x6

Info (12023): Found entity 1: mult6x6

Warning (12125): Using design file fifo_wrbuffer_512x16.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: fifo_wrbuffer_512x16

Info (12023): Found entity 1: fifo_wrbuffer_512x16

Warning (12125): Using design file wr_sdram.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: wr_sdram

Info (12023): Found entity 1: wr_sdram

Warning (12125): Using design file sdram_if.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: sdram_if

Info (12023): Found entity 1: sdram_if

Warning (12125): Using design file rd_sdram.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: rd_sdram

Info (12023): Found entity 1: rd_sdram

Warning (12125): Using design file fifo_display_1024x16.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: fifo_display_1024x16

Info (12023): Found entity 1: fifo_display_1024x16

Warning (12125): Using design file vga.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: vga

Info (12023): Found entity 1: vga

Warning (12125): Using design file i2c_av_config.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: I2C_AV_Config

Info (12023): Found entity 1: I2C_AV_Config

Warning (12125): Using design file i2c_controller.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project

Info (12023): Found entity 1: I2C_Controller

Info (12023): Found entity 1: I2C_Controller

Warning (10230): Verilog HDL assignment warning at i2c_controller.v(79): truncated value with size 32 to match size of target (1)

Warning (10230): Verilog HDL assignment warning at i2c_controller.v(91): truncated value with size 32 to match size of target (8)

Warning (12241): 8 hierarchies have connectivity warnings - see the Connectivity Checks report folder

Warning (13024): Output pins are stuck at VCC or GND

Warning (13410): Pin "sdram_addr[12]" is stuck at GND

Warning (13410): Pin "sdr_cke[0]" is stuck at VCC

Warning (13410): Pin "sdr_cs[0]" is stuck at GND

Warning (13410): Pin "sdr_dqm[0]" is stuck at GND

Warning (13410): Pin "sdr_dqm[1]" is stuck at GND

Warning (13410): Pin "leds[0]" is stuck at GND

Warning (13410): Pin "leds[1]" is stuck at GND

Warning (13410): Pin "leds[2]" is stuck at GND

Warning (13410): Pin "leds[3]" is stuck at GND

Warning (13410): Pin "leds[4]" is stuck at GND

Warning (13410): Pin "leds[5]" is stuck at GND

Warning (13410): Pin "sdram_addr[12]" is stuck at GND

Warning (13410): Pin "sdr_cke[0]" is stuck at VCC

Warning (13410): Pin "sdr_cs[0]" is stuck at GND

Warning (13410): Pin "sdr_dqm[0]" is stuck at GND

Warning (13410): Pin "sdr_dqm[1]" is stuck at GND

Warning (13410): Pin "leds[0]" is stuck at GND

Warning (13410): Pin "leds[1]" is stuck at GND

Warning (13410): Pin "leds[2]" is stuck at GND

Warning (13410): Pin "leds[3]" is stuck at GND

Warning (13410): Pin "leds[4]" is stuck at GND

Warning (13410): Pin "leds[5]" is stuck at GND

Warning (15536): Implemented PLL "pll_xscale:pll_xscale_inst|altpll:altpll_component|pll" as Cyclone IV E PLL type, but with warnings

Warning (15567): Can‘t achieve requested Medium bandwidth type; current PLL requires a bandwidth value of between 0.500 Mhz and 2.000 Mhz -- achieved bandwidth of 0.45 MHz to 0.59 MHz

Warning (15559): Can‘t achieve requested value 142.2 degrees for clock output pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk2 of parameter phase shift -- achieved value of 144.0 degrees

Info (15099): Implementing clock multiplication of 3, clock division of 2, and phase shift of 45 degrees (3086 ps) for pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 port

Info (15099): Implementing clock multiplication of 9, clock division of 2, and phase shift of 0 degrees (0 ps) for pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 port

Info (15099): Implementing clock multiplication of 9, clock division of 2, and phase shift of 144 degrees (3292 ps) for pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk2 port

Warning (15567): Can‘t achieve requested Medium bandwidth type; current PLL requires a bandwidth value of between 0.500 Mhz and 2.000 Mhz -- achieved bandwidth of 0.45 MHz to 0.59 MHz

Warning (15559): Can‘t achieve requested value 142.2 degrees for clock output pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk2 of parameter phase shift -- achieved value of 144.0 degrees

Info (15099): Implementing clock multiplication of 3, clock division of 2, and phase shift of 45 degrees (3086 ps) for pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 port

Info (15099): Implementing clock multiplication of 9, clock division of 2, and phase shift of 0 degrees (0 ps) for pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 port

Info (15099): Implementing clock multiplication of 9, clock division of 2, and phase shift of 144 degrees (3292 ps) for pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk2 port

Warning (15714): Some pins have incomplete I/O assignments. Refer to the I/O Assignment Warnings report for details

Warning (332174): Ignored filter at action_vip.sdc(49): pll_sys_inst|altpll_component|pll|inclk[0] could not be matched with a pin

Warning (332174): Ignored filter at action_vip.sdc(49): pll_sys_inst|altpll_component|pll|clk[0] could not be matched with a pin

Warning (332049): Ignored create_generated_clock at action_vip.sdc(49): Argument <targets> is an empty collection

Info (332050): create_generated_clock -name {pll_sys:pll_sys_inst|altpll:altpll_component|_clk0} -source [get_pins {pll_sys_inst|altpll_component|pll|inclk[0]}] -duty_cycle 50.000 -multiply_by 25 -divide_by 3 -master_clock {clk} [get_pins {pll_sys_inst|altpll_component|pll|clk[0]}]

Info (332050): create_generated_clock -name {pll_sys:pll_sys_inst|altpll:altpll_component|_clk0} -source [get_pins {pll_sys_inst|altpll_component|pll|inclk[0]}] -duty_cycle 50.000 -multiply_by 25 -divide_by 3 -master_clock {clk} [get_pins {pll_sys_inst|altpll_component|pll|clk[0]}]

Warning (332049): Ignored create_generated_clock at action_vip.sdc(49): Argument -source is an empty collection

Warning (332174): Ignored filter at action_vip.sdc(50): pll_sys_inst|altpll_component|pll|clk[1] could not be matched with a pin

Warning (332049): Ignored create_generated_clock at action_vip.sdc(50): Argument <targets> is an empty collection

Info (332050): create_generated_clock -name {pll_sys:pll_sys_inst|altpll:altpll_component|_clk1} -source [get_pins {pll_sys_inst|altpll_component|pll|inclk[0]}] -duty_cycle 50.000 -multiply_by 25 -divide_by 3 -phase 60.000 -master_clock {clk} [get_pins {pll_sys_inst|altpll_component|pll|clk[1]}]

Info (332050): create_generated_clock -name {pll_sys:pll_sys_inst|altpll:altpll_component|_clk1} -source [get_pins {pll_sys_inst|altpll_component|pll|inclk[0]}] -duty_cycle 50.000 -multiply_by 25 -divide_by 3 -phase 60.000 -master_clock {clk} [get_pins {pll_sys_inst|altpll_component|pll|clk[1]}]

Warning (332049): Ignored create_generated_clock at action_vip.sdc(50): Argument -source is an empty collection

Warning (332174): Ignored filter at action_vip.sdc(83): pll_sys:pll_sys_inst|altpll:altpll_component|_clk0 could not be matched with a clock

Warning (332174): Ignored filter at action_vip.sdc(83): pll_sys:pll_sys_inst|altpll:altpll_component|_clk1 could not be matched with a clock

Warning (332174): Ignored filter at action_vip.sdc(90): *ws_dgrp|dffpipe_re9:dffpipe20|dffe21a* could not be matched with a keeper

Warning (332049): Ignored set_false_path at action_vip.sdc(90): Argument <to> is an empty collection

Info (332050): set_false_path -from [get_keepers {*rdptr_g*}] -to [get_keepers {*ws_dgrp|dffpipe_re9:dffpipe20|dffe21a*}]

Info (332050): set_false_path -from [get_keepers {*rdptr_g*}] -to [get_keepers {*ws_dgrp|dffpipe_re9:dffpipe20|dffe21a*}]

Warning (332174): Ignored filter at action_vip.sdc(91): *rs_dgwp|dffpipe_qe9:dffpipe16|dffe17a* could not be matched with a keeper

Warning (332049): Ignored set_false_path at action_vip.sdc(91): Argument <to> is an empty collection

Info (332050): set_false_path -from [get_keepers {*delayed_wrptr_g*}] -to [get_keepers {*rs_dgwp|dffpipe_qe9:dffpipe16|dffe17a*}]

Info (332050): set_false_path -from [get_keepers {*delayed_wrptr_g*}] -to [get_keepers {*rs_dgwp|dffpipe_qe9:dffpipe16|dffe17a*}]

Warning (332060): Node: video_process:TV_Box|bt656_rx:bt656_rx_inst|lcc2 was determined to be a clock but was found without an associated clock assignment.

Warning (332060): Node: I2C_AV_Config:I2C_AV_Config_inst|mI2C_CTRL_CLK was determined to be a clock but was found without an associated clock assignment.

Warning (332056): PLL cross checking found inconsistent PLL clock settings:

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 was found on node: pll_xscale_inst|altpll_component|pll|clk[0] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 was found on node: pll_xscale_inst|altpll_component|pll|clk[1] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): Node: pll_xscale_inst|altpll_component|pll|clk[2] was found missing 1 generated clock that corresponds to a base clock with a period of: 37.037

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 was found on node: pll_xscale_inst|altpll_component|pll|clk[0] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 was found on node: pll_xscale_inst|altpll_component|pll|clk[1] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): Node: pll_xscale_inst|altpll_component|pll|clk[2] was found missing 1 generated clock that corresponds to a base clock with a period of: 37.037

Warning (15064): PLL "pll_xscale:pll_xscale_inst|altpll:altpll_component|pll" output port clk[0] feeds output pin "vga_clk~output" via non-dedicated routing -- jitter performance depends on switching rate of other design elements. Use PLL dedicated clock outputs to ensure jitter performance

Warning (15064): PLL "pll_xscale:pll_xscale_inst|altpll:altpll_component|pll" output port clk[2] feeds output pin "sdr_clk[0]~output" via non-dedicated routing -- jitter performance depends on switching rate of other design elements. Use PLL dedicated clock outputs to ensure jitter performance

Warning (169177): 28 pins must meet Altera requirements for 3.3-, 3.0-, and 2.5-V interfaces. For more information, refer to AN 447: Interfacing Cyclone IV E Devices with 3.3/3.0/2.5-V LVTTL/LVCMOS I/O Systems.

Info (169178): Pin sdram_data[0] uses I/O standard 3.3-V LVTTL at 58

Info (169178): Pin sdram_data[1] uses I/O standard 3.3-V LVTTL at 55

Info (169178): Pin sdram_data[2] uses I/O standard 3.3-V LVTTL at 54

Info (169178): Pin sdram_data[3] uses I/O standard 3.3-V LVTTL at 53

Info (169178): Pin sdram_data[4] uses I/O standard 3.3-V LVTTL at 52

Info (169178): Pin sdram_data[5] uses I/O standard 3.3-V LVTTL at 51

Info (169178): Pin sdram_data[6] uses I/O standard 3.3-V LVTTL at 50

Info (169178): Pin sdram_data[7] uses I/O standard 3.3-V LVTTL at 49

Info (169178): Pin sdram_data[8] uses I/O standard 3.3-V LVTTL at 112

Info (169178): Pin sdram_data[9] uses I/O standard 3.3-V LVTTL at 111

Info (169178): Pin sdram_data[10] uses I/O standard 3.3-V LVTTL at 110

Info (169178): Pin sdram_data[11] uses I/O standard 3.3-V LVTTL at 106

Info (169178): Pin sdram_data[12] uses I/O standard 3.3-V LVTTL at 105

Info (169178): Pin sdram_data[13] uses I/O standard 3.3-V LVTTL at 104

Info (169178): Pin sdram_data[14] uses I/O standard 3.3-V LVTTL at 103

Info (169178): Pin sdram_data[15] uses I/O standard 3.3-V LVTTL at 101

Info (169178): Pin i2c_data uses I/O standard 3.3-V LVTTL at 142

Info (169178): Pin reset_n uses I/O standard 3.3-V LVTTL at 91

Info (169178): Pin bt656_clk_27m uses I/O standard 3.3-V LVTTL at 88

Info (169178): Pin clk uses I/O standard 3.3-V LVTTL at 23

Info (169178): Pin bt656_data[5] uses I/O standard 3.3-V LVTTL at 67

Info (169178): Pin bt656_data[0] uses I/O standard 3.3-V LVTTL at 72

Info (169178): Pin bt656_data[1] uses I/O standard 3.3-V LVTTL at 73

Info (169178): Pin bt656_data[2] uses I/O standard 3.3-V LVTTL at 71

Info (169178): Pin bt656_data[6] uses I/O standard 3.3-V LVTTL at 68

Info (169178): Pin bt656_data[3] uses I/O standard 3.3-V LVTTL at 69

Info (169178): Pin bt656_data[4] uses I/O standard 3.3-V LVTTL at 70

Info (169178): Pin bt656_data[7] uses I/O standard 3.3-V LVTTL at 65

Info (169178): Pin sdram_data[0] uses I/O standard 3.3-V LVTTL at 58

Info (169178): Pin sdram_data[1] uses I/O standard 3.3-V LVTTL at 55

Info (169178): Pin sdram_data[2] uses I/O standard 3.3-V LVTTL at 54

Info (169178): Pin sdram_data[3] uses I/O standard 3.3-V LVTTL at 53

Info (169178): Pin sdram_data[4] uses I/O standard 3.3-V LVTTL at 52

Info (169178): Pin sdram_data[5] uses I/O standard 3.3-V LVTTL at 51

Info (169178): Pin sdram_data[6] uses I/O standard 3.3-V LVTTL at 50

Info (169178): Pin sdram_data[7] uses I/O standard 3.3-V LVTTL at 49

Info (169178): Pin sdram_data[8] uses I/O standard 3.3-V LVTTL at 112

Info (169178): Pin sdram_data[9] uses I/O standard 3.3-V LVTTL at 111

Info (169178): Pin sdram_data[10] uses I/O standard 3.3-V LVTTL at 110

Info (169178): Pin sdram_data[11] uses I/O standard 3.3-V LVTTL at 106

Info (169178): Pin sdram_data[12] uses I/O standard 3.3-V LVTTL at 105

Info (169178): Pin sdram_data[13] uses I/O standard 3.3-V LVTTL at 104

Info (169178): Pin sdram_data[14] uses I/O standard 3.3-V LVTTL at 103

Info (169178): Pin sdram_data[15] uses I/O standard 3.3-V LVTTL at 101

Info (169178): Pin i2c_data uses I/O standard 3.3-V LVTTL at 142

Info (169178): Pin reset_n uses I/O standard 3.3-V LVTTL at 91

Info (169178): Pin bt656_clk_27m uses I/O standard 3.3-V LVTTL at 88

Info (169178): Pin clk uses I/O standard 3.3-V LVTTL at 23

Info (169178): Pin bt656_data[5] uses I/O standard 3.3-V LVTTL at 67

Info (169178): Pin bt656_data[0] uses I/O standard 3.3-V LVTTL at 72

Info (169178): Pin bt656_data[1] uses I/O standard 3.3-V LVTTL at 73

Info (169178): Pin bt656_data[2] uses I/O standard 3.3-V LVTTL at 71

Info (169178): Pin bt656_data[6] uses I/O standard 3.3-V LVTTL at 68

Info (169178): Pin bt656_data[3] uses I/O standard 3.3-V LVTTL at 69

Info (169178): Pin bt656_data[4] uses I/O standard 3.3-V LVTTL at 70

Info (169178): Pin bt656_data[7] uses I/O standard 3.3-V LVTTL at 65

Warning (332174): Ignored filter at action_vip.sdc(49): pll_sys_inst|altpll_component|pll|inclk[0] could not be matched with a pin

Warning (332174): Ignored filter at action_vip.sdc(49): pll_sys_inst|altpll_component|pll|clk[0] could not be matched with a pin

Warning (332049): Ignored create_generated_clock at action_vip.sdc(49): Argument <targets> is an empty collection

Info (332050): create_generated_clock -name {pll_sys:pll_sys_inst|altpll:altpll_component|_clk0} -source [get_pins {pll_sys_inst|altpll_component|pll|inclk[0]}] -duty_cycle 50.000 -multiply_by 25 -divide_by 3 -master_clock {clk} [get_pins {pll_sys_inst|altpll_component|pll|clk[0]}]

Info (332050): create_generated_clock -name {pll_sys:pll_sys_inst|altpll:altpll_component|_clk0} -source [get_pins {pll_sys_inst|altpll_component|pll|inclk[0]}] -duty_cycle 50.000 -multiply_by 25 -divide_by 3 -master_clock {clk} [get_pins {pll_sys_inst|altpll_component|pll|clk[0]}]

Warning (332049): Ignored create_generated_clock at action_vip.sdc(49): Argument -source is an empty collection

Warning (332174): Ignored filter at action_vip.sdc(50): pll_sys_inst|altpll_component|pll|clk[1] could not be matched with a pin

Warning (332049): Ignored create_generated_clock at action_vip.sdc(50): Argument <targets> is an empty collection

Info (332050): create_generated_clock -name {pll_sys:pll_sys_inst|altpll:altpll_component|_clk1} -source [get_pins {pll_sys_inst|altpll_component|pll|inclk[0]}] -duty_cycle 50.000 -multiply_by 25 -divide_by 3 -phase 60.000 -master_clock {clk} [get_pins {pll_sys_inst|altpll_component|pll|clk[1]}]

Info (332050): create_generated_clock -name {pll_sys:pll_sys_inst|altpll:altpll_component|_clk1} -source [get_pins {pll_sys_inst|altpll_component|pll|inclk[0]}] -duty_cycle 50.000 -multiply_by 25 -divide_by 3 -phase 60.000 -master_clock {clk} [get_pins {pll_sys_inst|altpll_component|pll|clk[1]}]

Warning (332049): Ignored create_generated_clock at action_vip.sdc(50): Argument -source is an empty collection

Warning (332174): Ignored filter at action_vip.sdc(83): pll_sys:pll_sys_inst|altpll:altpll_component|_clk0 could not be matched with a clock

Warning (332174): Ignored filter at action_vip.sdc(83): pll_sys:pll_sys_inst|altpll:altpll_component|_clk1 could not be matched with a clock

Warning (332174): Ignored filter at action_vip.sdc(90): *ws_dgrp|dffpipe_re9:dffpipe20|dffe21a* could not be matched with a keeper

Warning (332049): Ignored set_false_path at action_vip.sdc(90): Argument <to> is an empty collection

Info (332050): set_false_path -from [get_keepers {*rdptr_g*}] -to [get_keepers {*ws_dgrp|dffpipe_re9:dffpipe20|dffe21a*}]

Info (332050): set_false_path -from [get_keepers {*rdptr_g*}] -to [get_keepers {*ws_dgrp|dffpipe_re9:dffpipe20|dffe21a*}]

Warning (332174): Ignored filter at action_vip.sdc(91): *rs_dgwp|dffpipe_qe9:dffpipe16|dffe17a* could not be matched with a keeper

Warning (332049): Ignored set_false_path at action_vip.sdc(91): Argument <to> is an empty collection

Info (332050): set_false_path -from [get_keepers {*delayed_wrptr_g*}] -to [get_keepers {*rs_dgwp|dffpipe_qe9:dffpipe16|dffe17a*}]

Info (332050): set_false_path -from [get_keepers {*delayed_wrptr_g*}] -to [get_keepers {*rs_dgwp|dffpipe_qe9:dffpipe16|dffe17a*}]

Warning (332060): Node: video_process:TV_Box|bt656_rx:bt656_rx_inst|lcc2 was determined to be a clock but was found without an associated clock assignment.

Warning (332060): Node: I2C_AV_Config:I2C_AV_Config_inst|mI2C_CTRL_CLK was determined to be a clock but was found without an associated clock assignment.

Warning (332056): PLL cross checking found inconsistent PLL clock settings:

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 was found on node: pll_xscale_inst|altpll_component|pll|clk[0] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 was found on node: pll_xscale_inst|altpll_component|pll|clk[1] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): Node: pll_xscale_inst|altpll_component|pll|clk[2] was found missing 1 generated clock that corresponds to a base clock with a period of: 37.037

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 was found on node: pll_xscale_inst|altpll_component|pll|clk[0] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 was found on node: pll_xscale_inst|altpll_component|pll|clk[1] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): Node: pll_xscale_inst|altpll_component|pll|clk[2] was found missing 1 generated clock that corresponds to a base clock with a period of: 37.037

Warning (332060): Node: video_process:TV_Box|bt656_rx:bt656_rx_inst|lcc2 was determined to be a clock but was found without an associated clock assignment.

Warning (332060): Node: I2C_AV_Config:I2C_AV_Config_inst|mI2C_CTRL_CLK was determined to be a clock but was found without an associated clock assignment.

Warning (332056): PLL cross checking found inconsistent PLL clock settings:

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 was found on node: pll_xscale_inst|altpll_component|pll|clk[0] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 was found on node: pll_xscale_inst|altpll_component|pll|clk[1] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): Node: pll_xscale_inst|altpll_component|pll|clk[2] was found missing 1 generated clock that corresponds to a base clock with a period of: 37.037

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 was found on node: pll_xscale_inst|altpll_component|pll|clk[0] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 was found on node: pll_xscale_inst|altpll_component|pll|clk[1] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): Node: pll_xscale_inst|altpll_component|pll|clk[2] was found missing 1 generated clock that corresponds to a base clock with a period of: 37.037

Warning (332060): Node: video_process:TV_Box|bt656_rx:bt656_rx_inst|lcc2 was determined to be a clock but was found without an associated clock assignment.

Warning (332060): Node: I2C_AV_Config:I2C_AV_Config_inst|mI2C_CTRL_CLK was determined to be a clock but was found without an associated clock assignment.

Warning (332056): PLL cross checking found inconsistent PLL clock settings:

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 was found on node: pll_xscale_inst|altpll_component|pll|clk[0] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 was found on node: pll_xscale_inst|altpll_component|pll|clk[1] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): Node: pll_xscale_inst|altpll_component|pll|clk[2] was found missing 1 generated clock that corresponds to a base clock with a period of: 37.037

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk0 was found on node: pll_xscale_inst|altpll_component|pll|clk[0] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): -multiply_by (expected: 3, found: 5), -divide_by (expected: 2, found: 9)

Warning (332056): -phase (expected: 45.00, found: 0.00)

Warning (332056): Clock: pll_xscale:pll_xscale_inst|altpll:altpll_component|_clk1 was found on node: pll_xscale_inst|altpll_component|pll|clk[1] with settings that do not match the following PLL specifications:

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): -multiply_by (expected: 9, found: 3), -divide_by (expected: 2, found: 2)

Warning (332056): Node: pll_xscale_inst|altpll_component|pll|clk[2] was found missing 1 generated clock that corresponds to a base clock with a period of: 37.037